Verilator가 5.xx 버젼으로 업데이트가 되었길래 관련 내용을 끄적여본다.

아래는 Verilator를 이용한 Tutorial이다. 이게 버젼 5.xx 부터는 개인 개발자뿐 아니라 여러 회사들까지 지원해서, 업그레이드가 되고 있는 것으로 보인다. 그리고, 이미 RISC-V등에서 Open source에서 사용하는 공식 simulator는 Verilator이기도 하고, 5.xx에서는 UVM지원들을 진행중이니 관심있게 봐도 좋을듯하다.

특징

verilator는 일단 verilog simulator와는 다른 점이 몇개 있다.

그중 하나는 cycle based simulator이다. 이 이야기는 #1 과 같은 delay구문이 동작하지 않고,

단지 clock에 의해서만 구동이 된다. 즉, 미묘한 타이밍 변화는 허용하지 않고 clock based로만 돌기때문에,

속도가 매우 빠르다. 이게 Thread수를 늘리면 왠만한 상용툴보다가도 더 빠르다고한다.

그래서 이부분은 약간 주의가 필요하며, 기존에 Verilog작성과도 차이가 있기때문에 이부분에 신경을 써야한다.

마찬가지로 icarus verilog는 cycle based simulator가 아니기 때문에 #1과 같은 구문이 동작한다.

우분투에서 verilator 5.xx를 최신으로 업데이트하고

이제, 기본적인 D FlipFlop을 테스트하는 예제를 작성해본다. (아래 내용들은 linux기반에서 작성된 내용들이다)

module dff (

input wire clk,

input wire rst,

input wire d,

output reg q

);

always @(posedge clk or posedge rst) begin

if (rst)

q <= 1'b0;

else

q <= d;

end

endmodule

test bench는 아래와 같이 임의로 작성하였다.

module tb_dff(

input clk,

input rst,

output q,

input d

);

// D-Flip-Flop 인스턴스화

dff u_d_ff(

.clk(clk),

.rst(rst),

.d(d),

.q(q)

);

endmodule

simulation을 위한 파일을 다음과 같이 컴파일한다. 여기에 vcd dump를 위해서 --trace 옵션을 추가한다.

verilator -Wall -cc --trace dff.v tb_dff.v --exe sim_main.cpp

아래는 sim_main.cpp 파일이다. 여기에도 마찬가지로 vcd를 덤프를 받기위해서 관련 구문들을 추가한다.

verilator는 앞서 설명한 cycle based simulator이기때문에 아래와 같은 c-bench를 이용해서 구동을 한다.

그래서 약간은 아래와 같은 C로 구동되는 부분에 대해서도 익숙해질 필요는 있어 보인다.

#include "Vtb_dff.h"

#include "verilated.h"

#include "verilated_vcd_c.h"

int main(int argc, char **argv) {

Verilated::commandArgs(argc, argv);

Vtb_dff* top = new Vtb_dff;

Verilated::traceEverOn(true);

VerilatedVcdC* tfp = new VerilatedVcdC;

top->trace(tfp, 99);

tfp->open("d_ff_tb.vcd");

vluint64_t time = 0;

const vluint64_t sim_time = 100;

while (time < sim_time) {

if (time < 5) {

top->rst = 1;

top->d = 0;

} else {

top->rst = 0;

//top->d = time % 2;

//top->d = !top->q;

}

top->clk = time % 2; // Clock toggle

top->d = !top->q;

top->eval();

tfp->dump(time);

time++;

}

tfp->close();

delete tfp;

delete top;

return 0;

}

verilator로 아래와 같이 실행파일을 만들고, 이를 수행한다. synopsys의 VCS와 수행법이 약간 비슷하다.

make -j -C obj_dir/ -f Vtb_dff.mk Vtb_dff

obj_dir/Vtb_dff

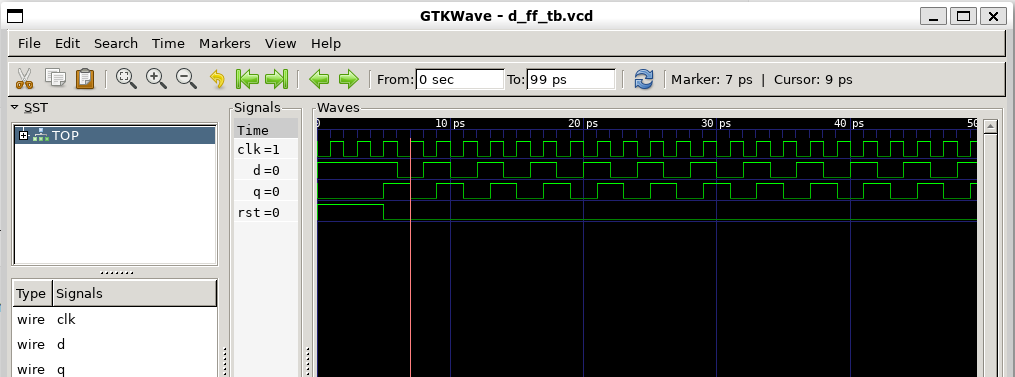

아래 수행한 결과는 gtkwave 로 파형을 열어본다. 상용툴보다는 못하지만, 이정도는 뭐 괜찮지 않을듯 싶다.