chisel은 한글로 하면 끌이라는 도구로 나무나 돌 얼음등을 긁는 도구이다.

RISC-V에서의 chisel은 scala 기반의 RTL Generator를 이야기하는 것이고 버클리에서 처음 만든 RISC-V가 이 chisel을 기반으로 생성되었다.

여기에 rocket chip generator라고, 단순히 하나의 model을 만드는것이 아니라 좀더 scalable하게 만들수 있는 구조이다. 이 기반이 되는 scala라는 language인데, 이게 저변은 그렇게 넓지는 않지만, 함수형언어로 완성도 측면에서는 완결성을 가지는 구조이기때문에, 결과물도 formal하게 나오는 것으로 보인다.

그래서 RISC-V에서 여러버젼이 있지만 이 rocket chip을 이용하려면 이 scala를 약간은 핸들링할수 있어야한다.

물론 우리 같은 사람들이 많기에 각 spec을 가지고 ibex라든지 pulp platform이라든지.

여러 변종이 있기때문에 꼭 rocket chip을 쓸 필요는 없다.

다만 이게 가장 시작이 되는 버젼이기도 하니 알아두면 나쁠것은 없다고 본다.

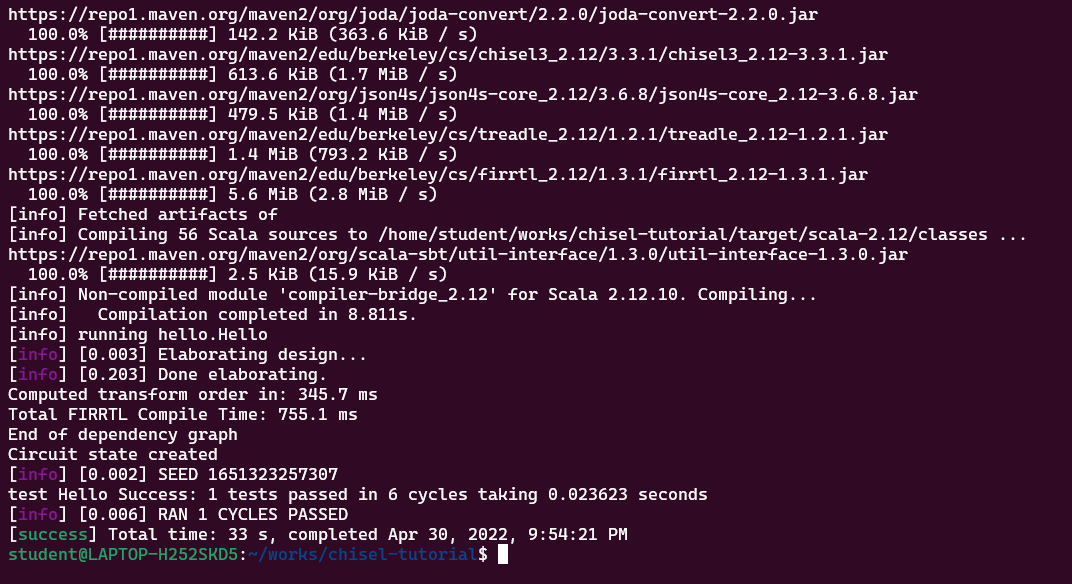

chisel tutorial 에 있는대로 아래와 같이 수행한다

git clone https://github.com/ucb-bar/chisel-tutorial.git

cd chisel-tutorial

git fetch origin

git checkout release여기서 sbt run을 하면 아래와 같이 1 Pass결과가 나온다.

(sbt는 online에서 없는 패키지들을 긁어 오기 때문에, online에서 실행시켜야 큰 불편함이 없다)

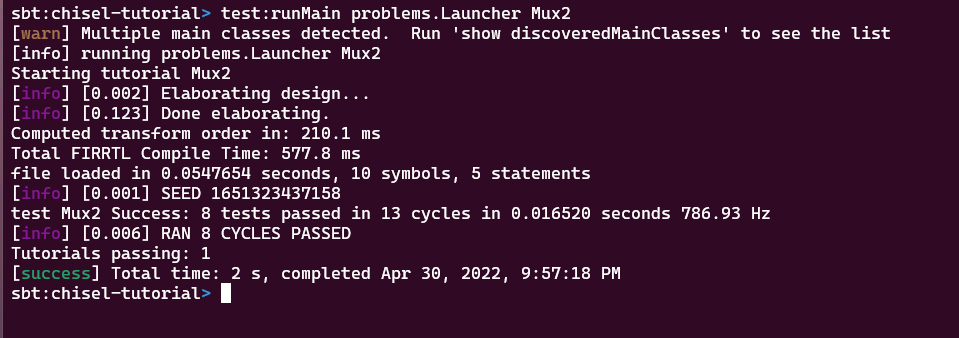

sbt로 아래와 같은 cli에 test:runMain problems.Launcher Mux를 입력하면 아래와 같이 수행이된다.

Mux2 를 테스트 한다.

Mux2는 Mux4.scala 안에 들어있고 scala 코드는 대략아래와 같다.

// See LICENSE.txt for license details.

package problems

import chisel3._

// Example:

//

// This is example of multiplexer 2-to-1 with 'sel' as control signal

// Multiplexed inputs are 'in0' and 'in1'

//

class Mux2 extends Module {

val io = IO(new Bundle {

val sel = Input(UInt(1.W))

val in0 = Input(UInt(1.W))

val in1 = Input(UInt(1.W))

val out = Output(UInt(1.W))

})

io.out := (io.sel & io.in1) | (~io.sel & io.in0)

}

// Problem:

//

// Build a 4-to-1 multiplexer out of three 2-to-1 multiplexers

// The first multiplexer is already done for you

//

class Mux4 extends Module {

val io = IO(new Bundle {

val in0 = Input(UInt(1.W))

val in1 = Input(UInt(1.W))

val in2 = Input(UInt(1.W))

val in3 = Input(UInt(1.W))

val sel = Input(UInt(2.W))

val out = Output(UInt(1.W))

})

val m0 = Module(new Mux2())

m0.io.sel := io.sel(0)

m0.io.in0 := io.in0

m0.io.in1 := io.in1

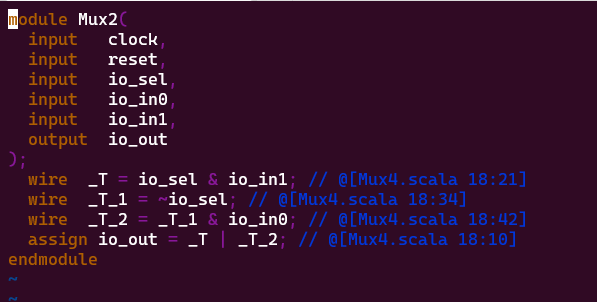

//Implement below ----------Mux2 의 FIRRTL과 Verilog 생성 결과는 아래와 같다.

이게 보다보면 중간 단계의 표현이 사람이 이해하기는 좀 어려운 감이 있긴하지만, 잘 나오는것 같다.

나온 RTL은 기계가 작성한 거라. 사실 가독성은 좀 떨어진다.

이것 바탕으로 RISC-V를 만들어내기때문에 익숙해지면 뭐 나쁘지 않을 듯 하다.

다만 이 scala라는 것 자체가 널리쓰이는 main stream은 아니기때문에, 언어의 완성도보다 익숙하지 않은 부분이 있어서, 접근하기가 쉽지 않을뿐이지, 이미 수학적 완성도를 바탕으로 한 영역으로 들어가고 있기때문에, 완성도 측면에서는 큰 차이는 없을듯하다.

'RISC-V' 카테고리의 다른 글

| [RISCV] Toolchain Install (0) | 2022.06.13 |

|---|---|

| [RISCV] Tang nano로 Hello RISC-V (0) | 2022.06.08 |

| [RISCV] Tang nano 9K (0) | 2022.05.29 |